• Register addressing

• Immediate addressing

• Direct addressing

• Register-indirect addressing

• Indexed addressing

• Implicit addressing

• Bit addressing

Addressing mode = Way of specifying operand

1. An instruction consists of

o Opcode (e.g., ADD, MOV,...) ~function

o Operand(s) (e.g., R3, #23H,...) ~ parameter

2. Where is the (value of) operand located?

o part of the instruction (immediate)

o in data memory (direct, indirect, indexed)

o in register; also, in a bit of a register/pin

Review: Register

1. 8-bit registers

o General purpose: R0, R1,... R7

o Special function: A, B, PSW, SP, I/O ports...

2. 16-bit registers

o DPTR (=DPH, DPL)

o PC is not an addressable register though

3. However! "Register addressing mode" refers to General Purpose one ONLY (R0..R7)

"Assembly" vs "Machine code" addressing mode

1. Book often assumes assembly-level

2. Strictly speaking, should be machine code representation of operand

3. Example: "register addressing mode"

o Machine level: R0...R7 only

o Assembly level: incl. all 8-bit reg, 16-bit

=>actually those are "direct mode"

Register addressing mode 8051

• Encoded as part of the instruction byte

• A is implicitly addressed; Rxxx is explicit

Immediate Addressing

• Immediate comes from "data value immediately follows the opcode byte"

o Meaning: constant value in an instruction

o Example:

Green part: immediate

Blue part : register

Immediate may be multiple bytes

1. Example: MOV imm to the 16-b data pointer

o MOV DPTR, #2550H ;; 2-byte immediate

o code is 3-bytes; 90 25 50

o DPTR is implicit

2. Assembler checks constant range

o MOV DPTR, #68975 ;; causes asm error

o #68975 is too large to fit in 2 bytes

Assembler label may be an immediate value

MOV DPTR, #Label

...

Label: DB "Hello world"

• The #Label part represents the address of the Label after the assembler determines its value

• fits the size of DPTR

Direct addressing

• Direct = address of operand

o on-chip memory

o Also mapped to general & special registers

o pointer in a separate byte, like immediates

• Usage: when you name a register not as R0...R7, but everything else that's addressable

o e.g., PSW, SP, I/O ports, DPH, DPL, address constant (as a label or constant)

Register vs Immediate vs direct addressing

• meaning of MOV A,0: take content at on-chip memory addr 0, copy it into the Accumulator

Subtle difference betw. Reg & Direct mode

1. MOV A, 0 ;;Direct mode => 2 bytes

o at on-chip address 0,

o mapped to R0 of bank 0 (four banks total)

2. MOV A, R0 ;;register mode =1 bytes!

o register R0 of current bank

o does not have to be bank zero!. Depends on PSW.3 and PSW.4

Special function registers

• Located at address >= 80H, up to FFH

o Also for Timer, Interrupt control, Serial port, Power control (not shown in table)

o Not all addresses are used

Implicit vs explicit direct addressing

• Accumulator has explicit address (E0H)

• Two ways: same functionality, but different encoding!

More example of implicit vs explicit:

• MOV DPTR, #2550H ;;3bytes

o This is implicit addressing for DPTR (DPTR does not have a direct address!)

• MOV DPL, #50H ;;3bytes

MOV DPH, #25H ;;3bytes

o DPL, DPH are explicitly direct addressing => each requires 1 bytes

o #50H, #25H each requires 1 byte

Implicit VS direct mode example cont'd

Limited combinations of addressing modes

• The opcode dictates operand's addr. modes

o Assembly mnemonic may look the same, but they may be different opcodes

Disallowed addr. mode combinations

• Register-to-register MOV

o e.g., MOV R1, R2

o solution: go through A or use immediate

• Accumulator to Accumulator MOV (useless)

• anything-to-immediate MOV (nonsense)

o e.g., MOV #20, R3

Addressing mode of PUSH/POP: direct mode

• Syntax:

o PUSH dir ;; push val at dir to stack

POP dir;; pop value to mem at dir

o Explicit: dir ;; on-chip mem location

o Implicit: SP (stack pointer)

• Example

o PUSH 05 ;; on-chip addr = 05

Cannot say PUSH R5 ;; register mode

Restrictions and Workarounds

• COL 3 : PUSH, POP are available only in direct mode

• Another idiosyncrasy of assembler: it could just translate

A =>0E 0H,

B =>0F 0H

Direct addressing VS indirect addressing

• Direct addressing (e.g, MOV A, 02)

o Pointer to operand is part of instruction (i.e., constant pointer, single-byte)

o example here: pointer = 02, 0n-chip memory

• ( Register ) Indirect (e.g., MOV A, @R0>

o Pointer to the operand value is found inside R0 or R1 (i.e., variable pointer)

o example here: pointer is found in R0

Register addressing vs Register-indirect addr

• Register addressing (e.g., MOV A, R1)

o R1 contains the operand value

• Register-indirect addressing (MOV A, @R1)

o R1 contains the pointer to operand value.

e.g., if R1 contains 20H, then operand is at on-chip memory address 20H

• R2,...R7 cannot be used with @

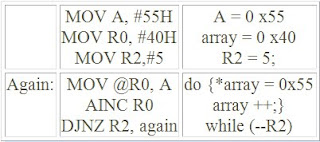

Example: Register vs Indirect mode

Copying constant to array: (1) direct

Copying constant to array: (2) indirect

Copying constant to array: (3) indirect + loop

Example: clear 16-byte array at address 60H

Example : loop 10 bytes *p++ = *q++;

Limitations of reg. indir. addressing in 8051

• For on-chip RAM only (1-byte pointer)

o 30H-7FH, SFR namely 80H -FFH

o Limited to R0 and R1 as pointers

• External RAM or on-chip ROM

o need to use DPTR (2-byte pointer)

Indexed Addressing Mode

• Index: array access

o Base address is in DPTR

o Index (offset) is in A

• Instruction in the form ;; regs are all implicit

o MOVC A, @A + DPTR

o C means "code memory"

• Meaning: A=DPTR [A];

Example LooKup Table: x-ssquared

• INT TAble []={0, 1, 4, 9, 16, 25, 36, 49, 64, 81};

for (;;) {P2 = Table [P1];}

• Assembly: Statically initialized array is DB:

Table: DB 0, 1, 4, 9, 16, 25, 36, 49, 64, 81

• Use DPTR for base pointer to Table:

MOV DPTR, #Table

• Lookup is

MOV A, P1 ;;P1 as index

MOVC A,@+DPTR ;;base +index

Program: write P2 = P1**2 continuosly

MOVC vs MOVX

• Both use 16-bit pointers

• MOVC: C= "code" space

• MOVX: X="external" data space

• Harvard architecture:

o separate code/data. e.g., 8051

• "Princeton" architecture:

o integrated code/data memory

Bit Addressing Mode

• Ability to specify a bit

o Normally, address are for bytes

• Bit addressable areas

o on-chip RAM at (byte-address) 20H--2FH each bit has a bit-address!

• I/0 ports P0...P3: 80H, 90H, A0H, B0H

• SFR: TCON, SCON, IE, IP, PSW, A, B, ACC

Wednesday, July 28, 2010

Wednesday, July 14, 2010

Session 4: I/O Port Programming

• General-purpose I/O ports

• Address/Data ports

• Dual role of P0,P2

• InterruptsBit/byte addressable

• IC TechnologiesFour I/O port

• 8-bits each P0, P1, P2, P3

• Ports are like registers

• Difference: value tied to the pins

• Bit addressable

What does a port look like?

1. Register tied to pin

2. Open collector output

o P0 has no internal pull up

o P1, P2, P3 have internal pull-up

3. Bit addressable and Byte addressable\

Output: Write to port register

1. Byte access

P1.7 P1.6 P1.5 P1.4 P1.3 P1.2 P1.1 P1.0

2. P1.7 is Most significant bit

P1.0 is Least significant bit

0 1 0 1 1 1 1 0

5 E

o MOV P1, #05EH

o Big-endian bit order

3. Bit access

o SETB P1.1 ;;sets port 1 bit 1

o CLR P2.3 ;; clears port 2 bit 3

for exampel in 7-Segment LED

• To write "0"

MOV P2, #7B ;; 0111 1011

• To Write "2"

MOV P2, #3D ;; 0011 1101

Input: reading from pins

1. Read pin value, not port-register value!!

o MOV A, P3 ;;read P3 pins, assign to A

2. Actually, pin & port may have different values

o A gets updated, but P3 register unchanged!

3. How to configure a port to input or output?

o Actually, it always outputs!

o Set port register to i if you want input!

example joystick input

1. First, P3 register should be 1111 1111

o Power-up default

2. Read P3 as a byte

o MOV A, P3

3. Read sigle bit (e.g up)

o MOV C, P3.0

Conflict between port register and pin

1. Register outputs 1 when input

2. Pin may input 0 or 1

3. Isn't this a short circuit?

o Actually, no

o input should "win"

4. Solution: open collector/open drain

o "weak 1" (overridable), "hard 0"

Bipolar vs MOS Transistors

Transistors are power controlled switches control signal=base or gate

Open collector/Open drain output

1. Off= connect to ground (0V)

2. On= "disconnect"

o Actually, "high impedance" (R2)

1. Voltage divider

o Vpin = Vcc * R2/(R1/R2)

o When R2>>R1, Vpin~~VCC

When R2= 0, Vpin~~0

Input value resolution

• Input pin = 1

o No conflict (register also pullup - 1)

=>read value = 1

• Input pin = 0

o register: pull-up to R1

o Vpin is pulled low by outside device

o R1 (10Kohm) draws current a price to pay, but logic works

Structure of Port P1

Reading a High value at input

Reading a Low value at Input pin

Port P0 is different from other I/0 ports

• No internal pull-up

o Ok as input

• Output --watch out!

o 0 is a real, hard zero

o 1 is a fake 1 (disconnect!)

• Solution

o Add external pull-up resistors

Structure of Port P0

Reasons for externalizing pullup

• Bus connection

o Multiple microcontrollers

o Bus pull-up, each MCU open collector

o "wired-AND" -- any zero pulls down bus

• Why not use built-in pull-up?

o Could be too many pull-ups!

o Pull-up too strong => hard to get clean 0

Example use of output with external pullup

• E.g., an LED

o Turn on when voltage difference > .7V

o I/O port voltage may be too high!

o Voltage divider => better matches voltage

• External pull-up voltage may be higher than MCU's output voltage

o Easy to "source" ("consume") current

What if port register bit = 0 during input?

• Could potentially short circuit!

o If input wire is tied to Vcc

• Solution: Always use pull-up

Three ways to avoid short circuit in input

• input switch with resistive pull-up

• input switch to ground

• input switch with a tristate

Alternative uses of P0, P2 pins

• For external memory

• P0 or AD0.. AD7

o address/data

o address : out

o data : in/out

• P2 or A15.. A8

o address: out

Alternative Uses of P3 pins

• For peripheral interface

o RxD, TxD: serial port

o INT0, INT11: interrupt

o T0, T1: timers

o WR, RD: memory

Example 4-1: toggle all bits every 1/4 second

ORG 0

BACK:

MOV A, #55

MOV P0, A

MOV P1, A

ACALL QSDELAY

MOV A, #AAH

MOV P0, A

MOV P1, A

ACALL QSDELAY

SJMP BACK

Timing control

• Q: How much to delay for "every 1/4"?

o Delay takes effect relative to the ACALL

o ACALL, SJMP, other overhead not handled

I/o bit manipulation

• Use bit instructions

o CPL P1.2 ;;complement port 1 bit 2

SETB P2.1 ;; assign port 2 bit 1 = 1

CLR P3.7 ;; assign port 3 bit 7 = 0

• Not all MCU instruction sets support bit op

o e.g., ATMEL AVR: access whole 8-bit port

P2 1 = 0 x 02; /*set P2.1 */

P3 & = 0 x 7F; /* clear P3.7 */

How to complement P1.2?

Duty cycle

• Percentage on time in a square wave

o 50% duty cycle

=> 50% on, 50% off

o 25% duty cycle

=> 25% on, 75% off

• Orthogonal to frequency

o each frequency can have diff. duty cycles

Application of duty cycling

• PWM: Pulse width modulation

o Use duty cycle to control average intensity

o Frequency should be sufficiently high

• Example

o motor speed

o brightness of light

Instructions

Rading input port

Example: polling

SETB P1.2

AGAIN: JNB P1.2, AGAIN

• Configure P.1 for input

• Keep looping as long as P1.2 ==0

=> waits till rising edge of P1.2

• Polling: keep checking I/0 in a loop Easy, fast but a little wasteful

• More "efficient" way: use interrupts

Use C as a general purpose bit register

• Carry flag (C) can be used as a bit register

• Alternative to previous polling code

Use MOV and JC/JNC

SETB P1.2

AGAIN: MOV C, P1.2

JNC AGAIN

Example: want to copy input bit to output

• Input P1.0, want to copy bit value to P2.7

• Cannot do

MOV P2.7, P1.0

=> no such instruction!

• Solution : use C as temporary

MOV C, P1.0

MOV P2.7, C

Reading from port-register instead of pin

Example of reading port register

• ANL P1, A ;; P1 :=P1 logical AND A

• This instruction has " read-modify-write" property

o Read a port register, modify the value, write back to the same port register

o All done "atomically" in one instruction

• Why is this a useful feature?

Atomic operation

• w/out read-modify-right, need 3 operations

o MOV A, P1

o ANL A, expression

o MOV P1, A

• But! if an interrupt occurs, value of A may be changed by the interrupt handler!

• Atomic means you can be sure operation is consistent even if interrupted

• Address/Data ports

• Dual role of P0,P2

• InterruptsBit/byte addressable

• IC TechnologiesFour I/O port

• 8-bits each P0, P1, P2, P3

• Ports are like registers

• Difference: value tied to the pins

• Bit addressable

What does a port look like?

1. Register tied to pin

2. Open collector output

o P0 has no internal pull up

o P1, P2, P3 have internal pull-up

3. Bit addressable and Byte addressable\

Output: Write to port register

1. Byte access

P1.7 P1.6 P1.5 P1.4 P1.3 P1.2 P1.1 P1.0

2. P1.7 is Most significant bit

P1.0 is Least significant bit

0 1 0 1 1 1 1 0

5 E

o MOV P1, #05EH

o Big-endian bit order

3. Bit access

o SETB P1.1 ;;sets port 1 bit 1

o CLR P2.3 ;; clears port 2 bit 3

for exampel in 7-Segment LED

• To write "0"

MOV P2, #7B ;; 0111 1011

• To Write "2"

MOV P2, #3D ;; 0011 1101

Input: reading from pins

1. Read pin value, not port-register value!!

o MOV A, P3 ;;read P3 pins, assign to A

2. Actually, pin & port may have different values

o A gets updated, but P3 register unchanged!

3. How to configure a port to input or output?

o Actually, it always outputs!

o Set port register to i if you want input!

example joystick input

1. First, P3 register should be 1111 1111

o Power-up default

2. Read P3 as a byte

o MOV A, P3

3. Read sigle bit (e.g up)

o MOV C, P3.0

Conflict between port register and pin

1. Register outputs 1 when input

2. Pin may input 0 or 1

3. Isn't this a short circuit?

o Actually, no

o input should "win"

4. Solution: open collector/open drain

o "weak 1" (overridable), "hard 0"

Bipolar vs MOS Transistors

Transistors are power controlled switches control signal=base or gate

Open collector/Open drain output

1. Off= connect to ground (0V)

2. On= "disconnect"

o Actually, "high impedance" (R2)

1. Voltage divider

o Vpin = Vcc * R2/(R1/R2)

o When R2>>R1, Vpin~~VCC

When R2= 0, Vpin~~0

Input value resolution

• Input pin = 1

o No conflict (register also pullup - 1)

=>read value = 1

• Input pin = 0

o register: pull-up to R1

o Vpin is pulled low by outside device

o R1 (10Kohm) draws current a price to pay, but logic works

Structure of Port P1

Reading a High value at input

Reading a Low value at Input pin

Port P0 is different from other I/0 ports

• No internal pull-up

o Ok as input

• Output --watch out!

o 0 is a real, hard zero

o 1 is a fake 1 (disconnect!)

• Solution

o Add external pull-up resistors

Structure of Port P0

Reasons for externalizing pullup

• Bus connection

o Multiple microcontrollers

o Bus pull-up, each MCU open collector

o "wired-AND" -- any zero pulls down bus

• Why not use built-in pull-up?

o Could be too many pull-ups!

o Pull-up too strong => hard to get clean 0

Example use of output with external pullup

• E.g., an LED

o Turn on when voltage difference > .7V

o I/O port voltage may be too high!

o Voltage divider => better matches voltage

• External pull-up voltage may be higher than MCU's output voltage

o Easy to "source" ("consume") current

What if port register bit = 0 during input?

• Could potentially short circuit!

o If input wire is tied to Vcc

• Solution: Always use pull-up

Three ways to avoid short circuit in input

• input switch with resistive pull-up

• input switch to ground

• input switch with a tristate

Alternative uses of P0, P2 pins

• For external memory

• P0 or AD0.. AD7

o address/data

o address : out

o data : in/out

• P2 or A15.. A8

o address: out

Alternative Uses of P3 pins

• For peripheral interface

o RxD, TxD: serial port

o INT0, INT11: interrupt

o T0, T1: timers

o WR, RD: memory

Example 4-1: toggle all bits every 1/4 second

ORG 0

BACK:

MOV A, #55

MOV P0, A

MOV P1, A

ACALL QSDELAY

MOV A, #AAH

MOV P0, A

MOV P1, A

ACALL QSDELAY

SJMP BACK

Timing control

• Q: How much to delay for "every 1/4"?

o Delay takes effect relative to the ACALL

o ACALL, SJMP, other overhead not handled

I/o bit manipulation

• Use bit instructions

o CPL P1.2 ;;complement port 1 bit 2

SETB P2.1 ;; assign port 2 bit 1 = 1

CLR P3.7 ;; assign port 3 bit 7 = 0

• Not all MCU instruction sets support bit op

o e.g., ATMEL AVR: access whole 8-bit port

P2 1 = 0 x 02; /*set P2.1 */

P3 & = 0 x 7F; /* clear P3.7 */

How to complement P1.2?

Duty cycle

• Percentage on time in a square wave

o 50% duty cycle

=> 50% on, 50% off

o 25% duty cycle

=> 25% on, 75% off

• Orthogonal to frequency

o each frequency can have diff. duty cycles

Application of duty cycling

• PWM: Pulse width modulation

o Use duty cycle to control average intensity

o Frequency should be sufficiently high

• Example

o motor speed

o brightness of light

Instructions

Rading input port

Example: polling

SETB P1.2

AGAIN: JNB P1.2, AGAIN

• Configure P.1 for input

• Keep looping as long as P1.2 ==0

=> waits till rising edge of P1.2

• Polling: keep checking I/0 in a loop Easy, fast but a little wasteful

• More "efficient" way: use interrupts

Use C as a general purpose bit register

• Carry flag (C) can be used as a bit register

• Alternative to previous polling code

Use MOV and JC/JNC

SETB P1.2

AGAIN: MOV C, P1.2

JNC AGAIN

Example: want to copy input bit to output

• Input P1.0, want to copy bit value to P2.7

• Cannot do

MOV P2.7, P1.0

=> no such instruction!

• Solution : use C as temporary

MOV C, P1.0

MOV P2.7, C

Reading from port-register instead of pin

Example of reading port register

• ANL P1, A ;; P1 :=P1 logical AND A

• This instruction has " read-modify-write" property

o Read a port register, modify the value, write back to the same port register

o All done "atomically" in one instruction

• Why is this a useful feature?

Atomic operation

• w/out read-modify-right, need 3 operations

o MOV A, P1

o ANL A, expression

o MOV P1, A

• But! if an interrupt occurs, value of A may be changed by the interrupt handler!

• Atomic means you can be sure operation is consistent even if interrupted

Session 3 : Looping

- Loops, Conditional jump instructions

- Conditions determeining conditional jump

- Unconditional long & short jumps

- Calculate target addresses for jumps

- using stack in subroutines

- Crystal frequenscy vs machine cycle

- Code programs to generate time delay

Looping ex.3-1

MOV A,#0 ;;init

MOV R2,#10

Again: ADD A,#03 ;;loop body

DJNZ R2,Again ;;while test

MOV R5,A ;;after loop

> init: A=0; R2=10;

> Loop: do {A+=3;} While (--R2!-0);

DJNZ means "decrement, jump if not zero"

> after: R5 = A;

Wednesday, June 30, 2010

Session 2: 8051 Assemble Language

• Register

• MOV • Power Up

• Stack

• PSW

• Register banks

Register Banks

1. General purpose, 8 bit

o A: (Accumulator), B 1. General purpose, 8 bit

o R0,R1, R2, R3, R4, R5, R6, R7

2. 16-bit, specifically used as pointers

o DPTR: (data pointer) : as 8-bit DPH, DPL (data pointer hi/low)

o PC: (Program Counter)1. Syntac:

Mov dest, src

o Think assignment statement: dest:=src;2. Dest src are called Operands

o Dest can be A, B, R0...R7, DPH, DPL

o Src can be A, B, R0...R7, or an immediate

3. Immediate = constant value, e.g as #12

Assembler idiosyncrasy with immediates

1. Default base: decimal

o #12 (assumed to be decimal)

o Can be hex: #12H (hex 12, = dec 18)2. However the char after # must be '0'.. '9'

o #FFH is invalid (since 'F' is not in '0'..'9'

o Solution: #0FFH (add a useless '0')

Immidiates vs direct (addressing mode)

o A= 0x17; #17H is literal

2. Mov a, 17

o A= * ((char *)17) 17 is an address

3. Big differenceo R0,...R7 => Register mode

o #17 => Immediate mode;

o 17 => direct mode (address -- where?)

Add instruction

1. ADD A, source

o Note: A is hardwired cannot use anything else

o Meaning: A:= A + source;

2. Source itself can be any R-Value operad

o Immediate, direct, register

How to write R2:= 0x25 + 0x35

1. Key: need to involve the accumulator A

2. MOV A, 25H ;; A: = 0x25;ADD A, 34H ;; A: = A + 0x34;

MOV R2, A ;; R2:= A;

3. Would be incorrect (in 8051) to try

MOV R2, 25H ;; this part is ok

ADD R2, 34H ;; must use A, not R2

4. Since the sum is constant, could doMOV R2, 59H ;; eval. by assembler

Assembly Language

1. Directives

o Commands to the assembler

e.g., starting address, allocate memory,...

2. (assembly) instructions

o Correspond to machine instructions

3. Labels

o Symbolic names that mark addresses

4. Comments

Example Program (2-1)

ORG 0H :start address

MOV R5, #25HMOV R7, #34H

MOV A, #0

ADD A, R5

ADD A, R7

ADD A, #12H

HERE: SJMP HEREEND ; some may be. END

Mnemonic

• A symbol that helps you remember

• example: phone number

o 2 = A, B, C 3 = D, E, F 4 = G, H, I

o doesn't need to be exact; can approximate

• Opcodes and directives are mnemonics

o MOV ~~ "move"

o JMP ~~ "jump" etc

Try this out

• Save assembly program as plain text file Name file.a51

• asem file.a51 ;;type this as a command

=> if correct, says no erross

• Output files -- simple case, sigle file

o .hex file: hex-formatted binary file

o .lst file: "listing" (before/after views)

.lst file by assmebler

Addr Machine code Assembly Source

0000 7D 25 Mov R5, #25H

0002 7D 34 Mov R7, #34H

0004 7F 00 Mov A, #0

0006 2D ADD A, R5

0007 2F ADD A, R7

0008 24 12 ADD A, #12H

000A 80 FE HERE: SJMP HERE

More assembler features

• Literal: in other bases

o Binary: add B after: 0000 1010B

• DB: define byte (or string, whatever data)

o store the data in program memory

o label is optional, not required!

• EQU: constant declaration (macro)o inlined when used. requires a macro name

Example of DB vs EQU

• DATA1: DB "Hello world"

DATA2: DB 25

=> both accupy space in (code) memory

• COUNT EQU 25 ;;occupies no space!

MOV R3, #COUNT

=> macro expansion into MOV R3, #25

- Sum = same as an Xor

- Carry = same as And

• Full adder

-Take Carry from prev bit

-Consists of two half adders

• Then connect them in a chain

• Forunately, VHDL can do bitvector add

PSW: program status word

• 8 bit register containing flags

o indicating status of the processor

CY (C bit) PSW.7 Carry flag

AC PSW.6 Auxiliary carry. for BCD arithmetic

F0, - PSW.5 (user)

RS1 PSW.4 Register bank select

RS0 PSW.3 Register bank select

OV PSW.2 Overflow

P PSW.0 Parity: even or odd # of i's in A

CY flag (C-bit)

• Carry out of the highest-order adder

o Does not mean overflow!!

Example: 0x01 + 0xFF = 0x00 with C= 1

(corresponds to 1 + (-1) = 0.)

o Carry or borrow, both have C=1

• Carry bit can be set, cleared, movedo CLR C ;; clear the C bit, means := 0

SETB C ;; set the C bit, means := 1

OV-flag (overflow)

• Overflow: too big/too small to represent

• ADD:

o Both operands same sign, sum different

e.g., both +, sum-; or both -, sum +

o Cannot overflow when operands mix + -

Because the sum is beween the two

• SUB:

o Opposite condition of ADD

Outcome of a signed A + B

• A and B have different signs

o Can't overflow. Because either

A≤ Sum ≤ B or B ≤ sum ≤ A

o V (overflow bit) is always '0' in this case.

• A and B have same signs

o Sum has same sign as A, B => No overflow

o Sum has a different sign => Overflow! (V='1')

Example of Overflow in signed addition

• Both A, B positive, Sum negative

• The status bits are

o V = 1 (overflow), C = 0 (no carry out),

o N = 1 (negative), Z = 0 (not zero)

Example of overflow in signed addition (cont'd)

• Both A, B negative, Sum positive

• The status bits are

o -V = 1 (overflow), C=1 (carry)

o N = 0 (not negative), z = 0 (not zero)

• Sum does not include the carry bit!!

Examples of NOT Overflow in signed addition

• A, B have different signs

• Overflow is not the same as arithmetic carry

o Truncating at the top is a feature, not a bug!

o C = 1 (ignored), V= 0, N = 0, Z = 0

Examples of unsigned addition

• MSB of A, B both = 0, MSB of Sum = 1

• the status bits are

o V = 0 (overflow), C = 0 (no carry out0,

o N = 0 (not negative), Z = 0 (not zero)

Examples of Overflow in unsigned additon (Cont'd)

• MSB of both A, B= 1, MSB of Sum = 0

• The status bits are

o V = 1 (overflow), C = 1 (carry)

o N = 0 (not negative), Z = 0 (not zero)

• Sum does not include the carry bit

Signed Subtract

• A - B = A + (-B)

o Take 2's complement of B (flip all bits, add 1)

o VHDL also provides the -operator

• N, Z, C, V bits

o C = "borrow", 1 when sign bit:

o if A, B same sign => V='0'

o if A, B diff signs and Res diff sign from A => V='1'

Examples of signed subtraction

• Positive A, Positive B, Negative Result

• The status bits are

o V = 0 (overflow), C = 1 (borrow).

o N = 1 (negative), Z = 0 (not zero).

Examples of overflow in signed subtraction

• Positive A, Negative B, Negative Result

• The status bits are

o V = 1 (overflow), C = 1 (borrow).

o N = 1 (negative), Z = 0 (not zero).

Unsigned Subtract

• A - B = A + (-B)

o Take 2's complement of B, add as before

o VHDL also provides the -operator

• N, Z, C, V bits

o N always '0' (unsigned).

o C = "borrow". Same as signed version

'1' when the MSB = table here

A 0 0 0 1

B 0 1 1 1

Res 1 1 0 1

o V unsigned = C unsigned

Examples of overflow in unsigned subtraction

• Both A, B Positive, Res negative

• C = 1 (ignored), V = 1, N = 0, Z = 0

A 0 0 0 1

B 0 1 1 1

Res 1 1 0 1

Register banks and Scratchpad memory

• Four register banks [ 00-lFH]

o 8 registers per bank (8 bytes/bank)

o bank 1 is stack

• Bit-addressable (16 bytes) [20-2FH]

• Scratchpad (Byte-addressable) [30-7FH]

• Total 128 bytes [00-7FH]

Register bank selection

• Register can be from 1 of 4 banks

o Depending on PSW.4, PSW.3

• Example

o MOV R0, #12H

Where is R0?

• Answer: depends on which bank!

o Could be address 00H, 08H, 10H, or 18H

Instruction for setting banks

• "Set a bit" (means assign the bit to 1)

o SETB PSW.4

• "Set a bit" (means assign the bit to 0)

o CLR PSW.3

• So, together, PSW.4 = 0, PSW.3 = 1

=> selects bank a

Two ways of accessing the same registers

• Register mode:

o Use R0, R1 ...name

o Current bank

o Need bank switching

• Direct mode:

o Use the RAM address of the register!

o 00 for R0 of bank 1, 12 for R2 of bank 3

Examples

• Register addressing:

SET B PSW.4

CLR PSW.3

MOV R3, #99H

• Direct addressing:

MOV 13, #99H

Stack

• Fundamental data structure in programming

o Return address of a call

o space for local (auto) variables

• Implicitly addressed

o PUSH (add element to stack)

o POP (remove element from stack)

• Need: stack pointer (SP) -- register in 8051

8051 architecture-supported stack

• 8-bit Stack Pointer SP

o Initialized to 07H on power up

=> points to just before R0 of bank1

• Grows from lower to higher address

o PUSH: pre-increment: stack [++SP]=d;

o POP: post-decrement: d=stack [SP--];

• Opposite from stacks on other CPUs!!

Synax of PUSH/Pop instructions

• PUSH 6

o This doesn't mean PUSH #6

o It means PUsh content of R6 to stack!

• POP 2

o Means pop the top element of stack to R2

o Reason: think "RAM Address"

Range of value for SP

• [07 - 1FH] (register bank 1, 2, 3)

o On power-up SP = 07H

o Should not go lower;

Could go up to 1FH (R7 of bank3)

• [30 - 7FH] (scratchpad memory)

• NOT [20 - 2FH] -- bit addressable area

Other use of stack : call /Return

• Call instruction

o pushes return address onto stack then go to target

• Return instruction

o pops return address then go to target

• Interrupt: hardware pushes return address

• Return-from-interrupt instruction

Subscribe to:

Posts (Atom)