• Register addressing

• Immediate addressing

• Direct addressing

• Register-indirect addressing

• Indexed addressing

• Implicit addressing

• Bit addressing

Addressing mode = Way of specifying operand

1. An instruction consists of

o Opcode (e.g., ADD, MOV,...) ~function

o Operand(s) (e.g., R3, #23H,...) ~ parameter

2. Where is the (value of) operand located?

o part of the instruction (immediate)

o in data memory (direct, indirect, indexed)

o in register; also, in a bit of a register/pin

Review: Register

1. 8-bit registers

o General purpose: R0, R1,... R7

o Special function: A, B, PSW, SP, I/O ports...

2. 16-bit registers

o DPTR (=DPH, DPL)

o PC is not an addressable register though

3. However! "Register addressing mode" refers to General Purpose one ONLY (R0..R7)

"Assembly" vs "Machine code" addressing mode

1. Book often assumes assembly-level

2. Strictly speaking, should be machine code representation of operand

3. Example: "register addressing mode"

o Machine level: R0...R7 only

o Assembly level: incl. all 8-bit reg, 16-bit

=>actually those are "direct mode"

Register addressing mode 8051

• Encoded as part of the instruction byte

• A is implicitly addressed; Rxxx is explicit

Immediate Addressing

• Immediate comes from "data value immediately follows the opcode byte"

o Meaning: constant value in an instruction

o Example:

Green part: immediate

Blue part : register

Immediate may be multiple bytes

1. Example: MOV imm to the 16-b data pointer

o MOV DPTR, #2550H ;; 2-byte immediate

o code is 3-bytes; 90 25 50

o DPTR is implicit

2. Assembler checks constant range

o MOV DPTR, #68975 ;; causes asm error

o #68975 is too large to fit in 2 bytes

Assembler label may be an immediate value

MOV DPTR, #Label

...

Label: DB "Hello world"

• The #Label part represents the address of the Label after the assembler determines its value

• fits the size of DPTR

Direct addressing

• Direct = address of operand

o on-chip memory

o Also mapped to general & special registers

o pointer in a separate byte, like immediates

• Usage: when you name a register not as R0...R7, but everything else that's addressable

o e.g., PSW, SP, I/O ports, DPH, DPL, address constant (as a label or constant)

Register vs Immediate vs direct addressing

• meaning of MOV A,0: take content at on-chip memory addr 0, copy it into the Accumulator

Subtle difference betw. Reg & Direct mode

1. MOV A, 0 ;;Direct mode => 2 bytes

o at on-chip address 0,

o mapped to R0 of bank 0 (four banks total)

2. MOV A, R0 ;;register mode =1 bytes!

o register R0 of current bank

o does not have to be bank zero!. Depends on PSW.3 and PSW.4

Special function registers

• Located at address >= 80H, up to FFH

o Also for Timer, Interrupt control, Serial port, Power control (not shown in table)

o Not all addresses are used

Implicit vs explicit direct addressing

• Accumulator has explicit address (E0H)

• Two ways: same functionality, but different encoding!

More example of implicit vs explicit:

• MOV DPTR, #2550H ;;3bytes

o This is implicit addressing for DPTR (DPTR does not have a direct address!)

• MOV DPL, #50H ;;3bytes

MOV DPH, #25H ;;3bytes

o DPL, DPH are explicitly direct addressing => each requires 1 bytes

o #50H, #25H each requires 1 byte

Implicit VS direct mode example cont'd

Limited combinations of addressing modes

• The opcode dictates operand's addr. modes

o Assembly mnemonic may look the same, but they may be different opcodes

Disallowed addr. mode combinations

• Register-to-register MOV

o e.g., MOV R1, R2

o solution: go through A or use immediate

• Accumulator to Accumulator MOV (useless)

• anything-to-immediate MOV (nonsense)

o e.g., MOV #20, R3

Addressing mode of PUSH/POP: direct mode

• Syntax:

o PUSH dir ;; push val at dir to stack

POP dir;; pop value to mem at dir

o Explicit: dir ;; on-chip mem location

o Implicit: SP (stack pointer)

• Example

o PUSH 05 ;; on-chip addr = 05

Cannot say PUSH R5 ;; register mode

Restrictions and Workarounds

• COL 3 : PUSH, POP are available only in direct mode

• Another idiosyncrasy of assembler: it could just translate

A =>0E 0H,

B =>0F 0H

Direct addressing VS indirect addressing

• Direct addressing (e.g, MOV A, 02)

o Pointer to operand is part of instruction (i.e., constant pointer, single-byte)

o example here: pointer = 02, 0n-chip memory

• ( Register ) Indirect (e.g., MOV A, @R0>

o Pointer to the operand value is found inside R0 or R1 (i.e., variable pointer)

o example here: pointer is found in R0

Register addressing vs Register-indirect addr

• Register addressing (e.g., MOV A, R1)

o R1 contains the operand value

• Register-indirect addressing (MOV A, @R1)

o R1 contains the pointer to operand value.

e.g., if R1 contains 20H, then operand is at on-chip memory address 20H

• R2,...R7 cannot be used with @

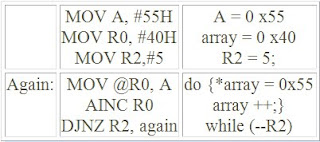

Example: Register vs Indirect mode

Copying constant to array: (1) direct

Copying constant to array: (2) indirect

Copying constant to array: (3) indirect + loop

Example: clear 16-byte array at address 60H

Example : loop 10 bytes *p++ = *q++;

Limitations of reg. indir. addressing in 8051

• For on-chip RAM only (1-byte pointer)

o 30H-7FH, SFR namely 80H -FFH

o Limited to R0 and R1 as pointers

• External RAM or on-chip ROM

o need to use DPTR (2-byte pointer)

Indexed Addressing Mode

• Index: array access

o Base address is in DPTR

o Index (offset) is in A

• Instruction in the form ;; regs are all implicit

o MOVC A, @A + DPTR

o C means "code memory"

• Meaning: A=DPTR [A];

Example LooKup Table: x-ssquared

• INT TAble []={0, 1, 4, 9, 16, 25, 36, 49, 64, 81};

for (;;) {P2 = Table [P1];}

• Assembly: Statically initialized array is DB:

Table: DB 0, 1, 4, 9, 16, 25, 36, 49, 64, 81

• Use DPTR for base pointer to Table:

MOV DPTR, #Table

• Lookup is

MOV A, P1 ;;P1 as index

MOVC A,@+DPTR ;;base +index

Program: write P2 = P1**2 continuosly

MOVC vs MOVX

• Both use 16-bit pointers

• MOVC: C= "code" space

• MOVX: X="external" data space

• Harvard architecture:

o separate code/data. e.g., 8051

• "Princeton" architecture:

o integrated code/data memory

Bit Addressing Mode

• Ability to specify a bit

o Normally, address are for bytes

• Bit addressable areas

o on-chip RAM at (byte-address) 20H--2FH each bit has a bit-address!

• I/0 ports P0...P3: 80H, 90H, A0H, B0H

• SFR: TCON, SCON, IE, IP, PSW, A, B, ACC